| REV. | ZONE | ECO# | REVISION           | APPD | DATE |

|------|------|------|--------------------|------|------|

| A    |      |      | PRODUCTION RELEASE |      |      |

#### NOTE:

MANUFACTURERS RECEIVING APPLE APPROVED VENDOR STATUS FOR THEIR PRODUCT UNDER THIS PART NUMBER PLEASE NOTE: You must not change your part design, materials or manufacturing process from those used for the original samples submitted to and approved by Apple without written approval of Apple. Proposed changes determined by Apple to be significant, will require the manufacturer to submit new samples and/or data for review and approval prior to product

| $\bigcirc \oplus \bigoplus$                                             | METRIC                                    |    |          |      | Apple Computer, Inc.                                                                                                                                       |  |  |  |  |

|-------------------------------------------------------------------------|-------------------------------------------|----|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DIMENSIONS ARE IN MILLIMETERS. DIMENSIONS IN BRACKETS () ARE IN INCHES. | BT // DESIGN CK //                        |    |          | //   | NOTICE OF PROPRIETARY PROPERTY THE INFORMATION CONTAINED HERRIN IS THE PROPRIETAR' PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR AGREES TO THE POLLOWING: |  |  |  |  |

| TOLERANCES  X.X ±3 [.01]                                                | ENG APPD                                  | // | MPG APPD | //   | (i) NOT TO REPRODUCE OR COPY IT                                                                                                                            |  |  |  |  |

| X.XX ±13 [.005]                                                         | QA APPD                                   | 11 | DESIGNER | //   | IC, CUSTOM SCSI DMA                                                                                                                                        |  |  |  |  |

| X.XXX ± .03 [.001]<br>ANGLEs ± .1                                       | RELEASE                                   | 11 | SCALE    |      | CONTROLLER, QFP-100                                                                                                                                        |  |  |  |  |

| or as noted                                                             | MATERIAL/FINISH<br>NOTED AS<br>APPLICABLE |    |          | SIZE | DRAWING NUMBER SHT                                                                                                                                         |  |  |  |  |

| DO NOT SCALE DRAWING                                                    |                                           |    |          | A    | 343S0064-A 1/31                                                                                                                                            |  |  |  |  |

#### **TABLE 1. NORMAL OPERATION MODE PIN PLACEMENT**

Note: Normal operation mode occurs when the TEST input (pin 65) is low.

| 1. VSS 2. MA(12 3. MA(13 4. MA(14 5. MA(15 6. D(0) 7. D(1) 8. D(2) 9. D(3) 10. VSS 11. D(4) 12. D(5) 13. D(6) 14. D(7) 15. D(8) 16. D(9) 17. D(10) 18. D(11) 19. VDD 20. VSS 21. D(12) 22. D(13) 23. D(14) 24. D(15) 25. D(16) | 27. D(18) 28. D(19) 29. VSS 30. D(20) 31. D(21) 32. D(22) 33. D(23) 34. D(24) 35. D(25) 36. D(26) 37. D(27) 38. VSS 39. D(28) 40. D(29) 41. D(30) 42. D(31) 43. /SD(1) 45. VSS 46. /SD(2) 47. /SD(3) 48. /SD(4) 49. /SD(5) | 51. /SD(6)<br>52. /SD(7)<br>53. /SDBP<br>54. /SATN<br>55. /SBSY<br>56. VSS<br>57. /SACK<br>58. /SRST<br>59. /SMSG<br>60. /SSEL<br>61. /SCD<br>62. VSS<br>63. /SREQ<br>64. /SIO<br>65. TEST<br>66. VDD<br>67. CPUCLK<br>68. /CS<br>69. /INT<br>70. /RESET<br>71. /BERBY<br>72. /BGACK<br>73. /BGOUT<br>74. /BGIN<br>75. /BR | 76. VSS 77. SIZ0 78. SIZ1 79. /DSACK0 80. /STERM 81. FC1 82. R/W 83. /DSACK1 84. /AS 85. /ABEN 86. /ALE 87. MA(0) 88. MA(1) 89. MA(2) 90. MA(3) 91. VDD 92. VSS 93. MA(4) 94. MA(5) 95. MA(6) 96. MA(7) 97. MA(8) 98. MA(9) 99. MA(10) 100. MA(11) |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| \ '                                                                                                                                                                                                                            | TABLE 2. NORMAL OPERATION                                                                                                                                                                                                  | ON MODE PIN DES                                                                                                                                                                                                                                                                                                            | GRIPTION [                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                                                                                                                                                                                                                | TABLE 2. / TOTALINA OF ETIAL                                                                                                                                                                                               | 011111000011111000                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| INPOTS                                                                                                                                                                                                                         |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| RESET                                                                                                                                                                                                                          | - Used to reset the SCSI DMA.                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| /CS<br>CPUCLK                                                                                                                                                                                                                  | - Chip Select. Used to select the - Clock signal to the SCSI DMA.                                                                                                                                                          | SCSI DMA during P                                                                                                                                                                                                                                                                                                          | IO (Programmed I/U) transfers.                                                                                                                                                                                                                     |  |  |  |  |  |  |

| /BGIN                                                                                                                                                                                                                          | - The assertion of /BGIN signals t                                                                                                                                                                                         | that the bus is to be                                                                                                                                                                                                                                                                                                      | given to a requesting                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                                                                                                                                                                                                                                | bus master when the curr                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                                                                                                                                                                                                                | when it can take the bus.                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                            | other signals to determine                                                                                                                                                                                                                         |  |  |  |  |  |  |

| TEST                                                                                                                                                                                                                           | - Allows the 53C80 host adapter of                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                            | ic internal to the SCSI DMA)                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                                                                                                                                                                                                                                | to be tested directly. See                                                                                                                                                                                                 | Section 6.2.3 for fur                                                                                                                                                                                                                                                                                                      | ther Test Mode information.                                                                                                                                                                                                                        |  |  |  |  |  |  |

| /BERR<br>/STERM                                                                                                                                                                                                                |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

#### **OUTPUTS**

/BGOUT

- The outgoing daisy chained bus grant line. The SCSI DMA will normally pass the signal /BGIN to /BGOUT unless it intends to become the next bus master. It then breaks the daisy chain and

negates /BGOUT.

/DSACK1 - Indicates the completion of a 32 bit PIO data transfer.

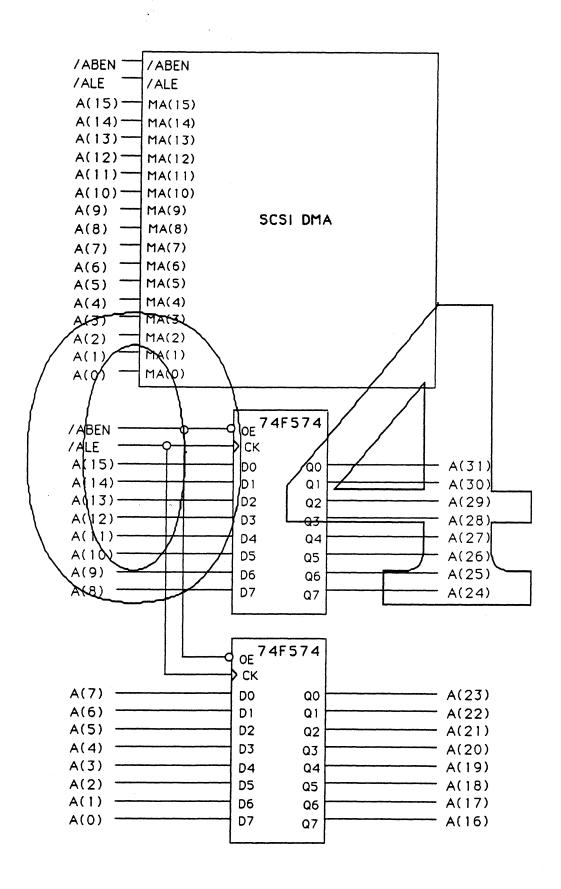

/ALE - During DMA operations, the rising edge of this signal is used to latch the 16 high order DMA address bits. This signal is to supply the clock input to the necessary external address - latching registers. (2 registers, such as 74F574's are required in a system to accomodate the multiplexed-address design of the SCSI DMA. See figure 5 for schematic.) /ABEN - During DMA transfers, this signal is used to enable the high order address bits onto the address bus. This signal is to supply the output enable input to the necessary external address-latching registers. MA[15-9,3-0] - With MA[8-4] forms the multiplexed address bus. /INT Interrupt signal from the SCSI DMA. (Open drain output, Timing specs derived from system with 3.3k pullup registers on open drain outputs.) /BR - The SCSI DMA requests bus mastership using this line. (Open drain output.) FC1 - Function code bit 1. (Used during DMA cycles. This bit is driven low to indicate a non-CPU space operation.) BIDIRECTIONAL Bidirectional 32 bit data bus used for both DMA and PIO transfers. Bidirectional bits of the multiplexed address bus. PIO Mode: Input to indicate register to be accessed during PIO transfers.

D[31-0] MA[8-4] DMA Mode: Output to form multiplexed address bus with MA[15-9] and MA[3-0]. /AS Indicates that valid address, size, and R/W information is on the bus. PIO Mode: Input driven by 68030. DMA Mode: Output. R/W Indicates a read (high) of write (low) direction. PIO Mode: Input driven by 68030. DMA Mode: Outbut. SIZ[1+0] Indicate the number of bytes to be transferred during a given bus cycle. PIO Mode: Input driven by 68030. DMA Mode: Output. /DSACK0 Indicates termination of an asynchronous data transfer. PIO Mode: Output. DMA Mode: Input driven by asynchronous memory controller. (/STERM terminated memory cycles afford better performance.) Indicates that an external device (not the CPU) has assumed /BGACK bus mastership. /SDB[7-0] - SCSI data bus. /SDBP - Odd data parity for the SCSI data bus. /SATN - Indicates an attention condition on the SCSI bus. /SBSY Indicates that the SCSI bus is being used. /SREQ - Indicates a request for a SCSI REQ/ACK data transfer. /SACK - Indicates an acknowledgement during a SCSI REQ/ACK data transfer. /SRST - Triggers SCSI bus reset. /SMSG - Indicates a message condition on the SCSI bus. /SSEL - Used by an initiator to select a target or by a target to reselect an initiator on the SCSI bus. /SCD - Indicates that control or data is on the SCSI bus. /SIO - Controls the direction of data movement on the SCSI bus. Also used to distinguish between selection and reselection phases.

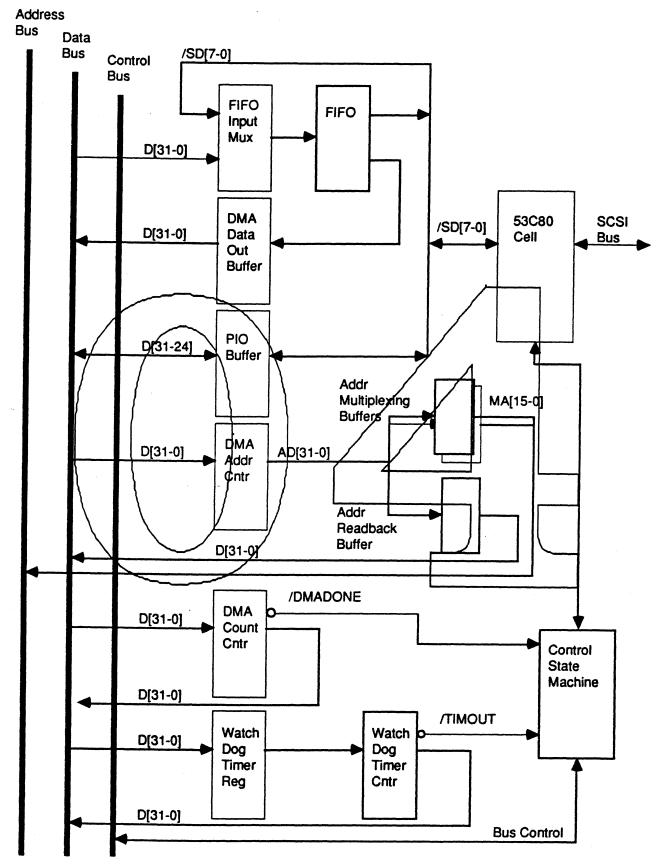

FIGURE 2. FLOW BLOCK DIAGRAM

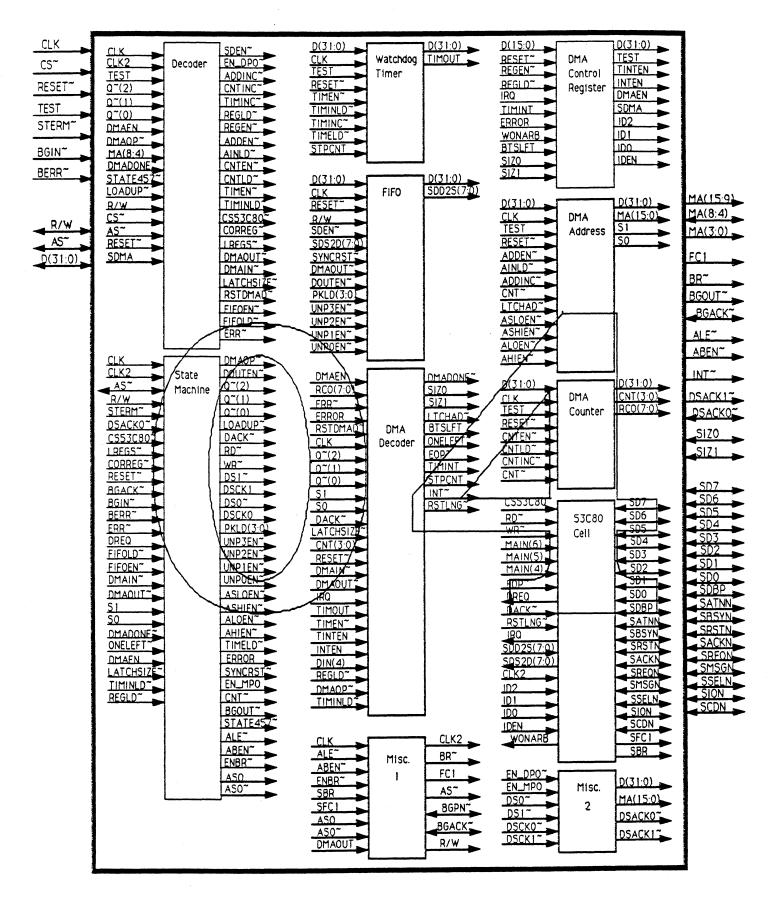

FIGURE 3. DETAILED BLOCK DIAGRAM

8

FIGURE 5. SCSI DMA WITH EXTERNAL ADDRESS REGISTERS SCHEMATIC

343S0064-A

### **TABLE 7. TIMING**

VDD = 4.75V to 5.25V, Temperature = 0 - 70°C, CL = 100pF Refer to figures 6 thru 10

| SIGNAL         |        | TIMING DESCRIPTION                       | SYMBOL     | MIN. | MAX.     | UNITS | FIG.     |

|----------------|--------|------------------------------------------|------------|------|----------|-------|----------|

| GENERAL TIM    | NG     |                                          |            | 1    | <u> </u> | 1     | <u> </u> |

| CPUCLK         | F      | requency                                 |            | Π    | 25       | MHz   | 6-10     |

|                |        | lock Period (ø)                          |            | 40   |          | ns    | 6-10     |

|                |        | lock high time                           | į          | 16   | i        | ns    | 6-10     |

|                |        | lock low time                            |            | 16   |          | ns    | 6-10     |

| /RESET         | Α      | ssertion time                            |            | 80   |          | ns    |          |

| /RESET         | D      | elay time from /RESET rising             |            | 8ø   |          | ns    |          |

|                | e      | dge to full operation                    |            |      |          |       |          |

| TEST           | D      | elay from TEST falling edge              |            |      | 40       | ns    |          |

|                |        | 53C80 inputs and outputs valid           |            |      |          |       |          |

|                |        | SCSI DMA pads                            |            |      |          |       |          |

| /AS            | 10     | PUCLK falling edge to /AS falling edg    |            | 3/   | 18       | ns    | 6-9      |

| /AS, R/W, MA[8 |        | etup to-/CS falling edge                 | t1         | /0   |          | ns    | 6-9      |

| /CS /          | F      | all setup to CPUCLK rising edge          | t2         | 20   |          | ns    | 6-9      |

| /_             | to     | be captured during that cycle            |            |      |          |       |          |

| /AS            |        | PUCLK falling\edge to /\S rising edg     |            | 9    | 18       | ns    | 6-9      |

| R/W, MA[8/4]   |        | old from /AS rising edge                 | 14/        | /2   | ļ        | ns    | 6-9      |

| /CS            | 14     | old from /AS rising edge                 | <b>(</b> 5 | 0    | 15       | ns    | 6-9      |

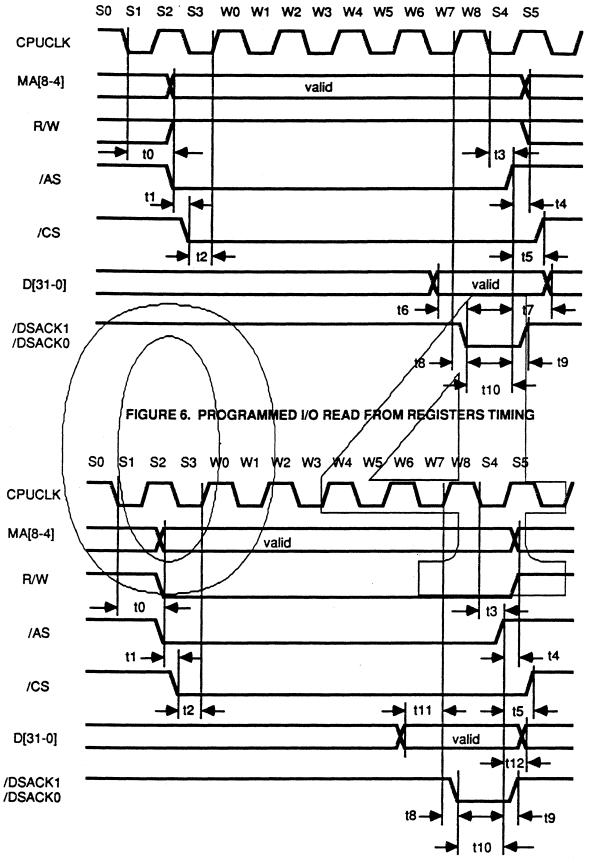

| \              |        | READ, WRITE FROM REGISTER TW             | IING       |      |          |       |          |

| DSACKO, IDSA   | CK1    | CPUCLK rising edge to DSACK falling edge | t8         |      | 30       | ns    | 6,7      |

| DSACKO,/DSA    | CK1    | AS rising edge to /DSACK rising edge     | t9         |      | 20       | ns    | 6,7      |

| AS             | $\Box$ | Hold time after /DSACK falling edge      | t10        | -20  | 2ø       | nis   | 6.7      |

| D[31-0]        | J      | Setup to /DSACK falling                  | t6         | 25   |          | ns    | 6        |

|                | 1      | edge                                     |            |      | ļ        |       |          |

| D[31-0]        |        | Hold from /AS rising edge                | 17         | 5    |          | ns    | 6        |

| 0[31-0]        |        | Setup to CPUCLK rising edge              | t11        | 20   |          | ns    | 7        |

| 0[31-0]        |        | Hold from /AS rising edge                | t12        | 0    |          | ns    | 7        |

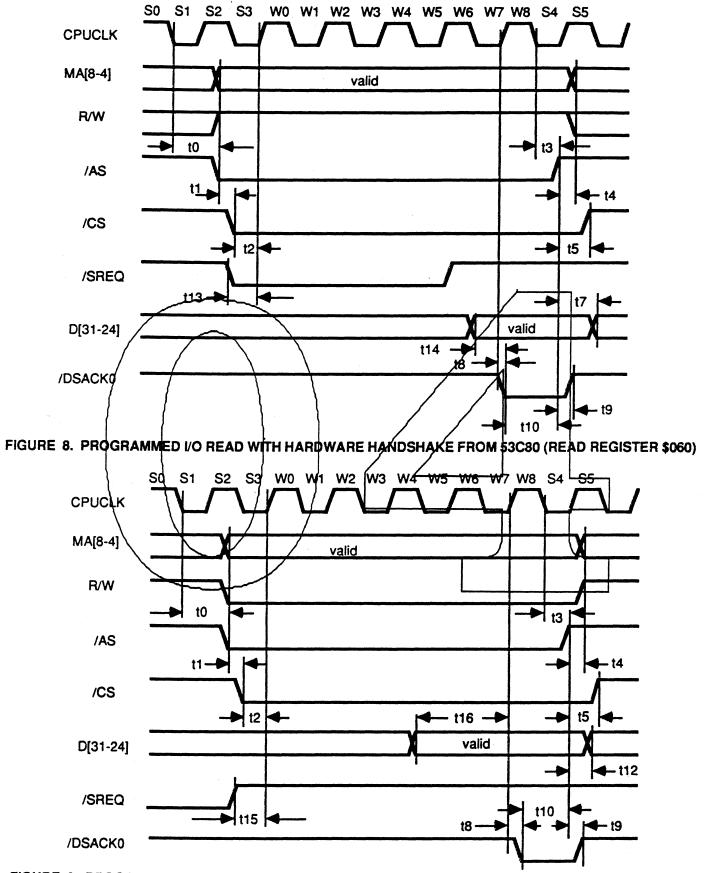

# PROGRAMMED I/O READ, WRITE WITH HARDWARE HANDSHAKE FROM/TO 53C80

| /DSACK0  | CPUCLK rising edge to /DSACK0 falling edge | t8  |    | 30 | ns | 6,7 |

|----------|--------------------------------------------|-----|----|----|----|-----|

| /DSACK0  | /AS rising edge to /DSACK0 rising edge     | t9  |    | 20 | ns | 8,9 |

| /AS      | Hold time after /DSACK0 falling edge       | t10 | 20 | 2ø | ns | 8.9 |

| /SREQ    | /SREQ falling edge to start of WO          | t13 | 3ø | 5ø | ns | 8   |

| D[31-24] | Setup to /DSACK0 falling edge              | t14 | 10 |    | ns | 8   |

| D[31-24] | Hold from /AS rising edge                  | t7  | 5  |    | ns | 8   |

| /SREQ    | /SREQ rising edge to start of WO           | t15 | 3ø | 5ø | ns | 9   |

| D[31-24] | Setup to CPUCLK rising edge                | t16 | 50 |    | ns | 9   |

| D[31-24] | Hold from /AS rising edge                  | t12 | 0  |    | ns | 9   |

TABLE 7. TIMING (CONT.)

VDD = 4.75V to 5.25V, Temperature = 0 - 70°C, CL = 100pF

Rpu = 3.3k - for open drain outputs /BR and /INT

Refer to figures 6 thru 10

| SIGNAL           | TIMING DESCRIPTION                                                            | SYM.       | MIN.       | MAX.         | UNITS                                            | FIG.     |

|------------------|-------------------------------------------------------------------------------|------------|------------|--------------|--------------------------------------------------|----------|

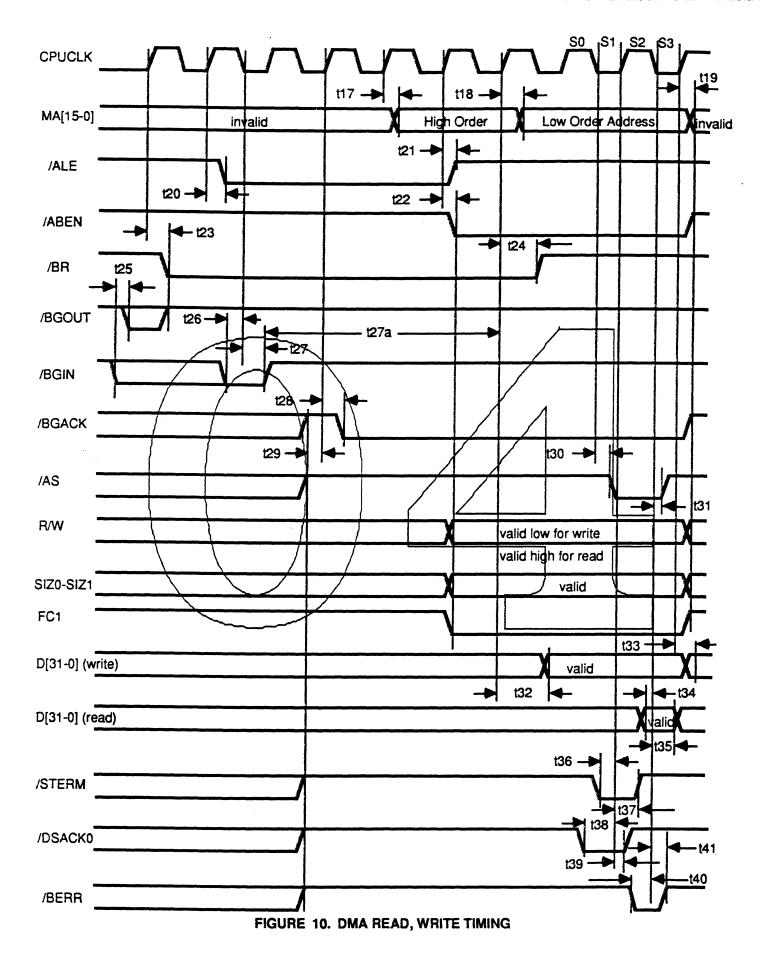

| DMA READ, WRITE  |                                                                               | O 1 141. 1 | 10011 10   | 1000 1011    |                                                  | 1        |

| /BR, /BGOUT      | CPUCLK rising edge to /BR                                                     | t23        |            | 40           | ns                                               | 10       |

| /BN,/BGCU1       | falling edge and /BGOUT rising edge                                           | 120        |            |              | 1                                                | 1.       |

| /ALE             | CPUCLK rising edge to /ALE                                                    | t20        |            | 45           | ns                                               | 10       |

| ALE              |                                                                               | ندن        |            | 10           |                                                  | '        |

| (DCIN)           | falling edge                                                                  | t26        | 20         |              | ns                                               | 10       |

| /BGIN            | Falling edge to CPUCLK falling edge                                           | 120        | 20         |              | '~                                               | '        |

| 00101            | (to be seen that cycle)                                                       | t28        |            | 65           | ns                                               | 10       |

| /BGACK           | CPUCLK rising edge to                                                         | 120        |            | 00           | 1                                                | 1.0      |

| 50401/ 440       | assertion of /BGACK                                                           | t29        |            | 20           | ns                                               | 10       |

| /BGACK, /AS      | Signal valid to CPUCLK                                                        | 129        |            | 20           | 113                                              | 1.0      |

| /STERM,          | rising edge (to be seen that cycle)                                           |            |            |              |                                                  | 1        |

| /DSACK0,/BERR    |                                                                               | 14 79      |            |              |                                                  | 10       |

| MA[15-0]         | CPUCLK rising edge to high                                                    | t17        |            | 55           | ns                                               | 110      |

|                  | order address valid                                                           |            |            | <del></del>  | <del>   </del>                                   | 140      |

| MA[15-0]         | PUCLK rising edge to high order address                                       | t18        |            | 50           | ns                                               | 10       |

|                  | invalid and low order address valid                                           |            |            |              |                                                  |          |

| /ALE             | CPUCLK rising edge to ALE rising edge                                         | t21        | /          | 40           | ns                                               | 10       |

| /ABEN, R/W, /    | CPVCLK rising adge to assertion                                               | t22        | Υ ".       | 45           | ns                                               | 10       |

| SIZ0, SIZ1, F¢1  | of ≴ignal \                                                                   |            |            |              |                                                  | <u> </u> |

| /BGOUT           | /BGIN assertion to /BGOUT assertion                                           | t25        |            | 40           | ns                                               | 10       |

| )                | (/BR deasserted)                                                              |            |            |              | <u> </u>                                         | <u> </u> |

| /BR              | CPUCLK rising edge to /BR rising edge                                         | 124        |            | 170          | ns                                               | 10       |

| /BGIN            | CPUCLK falling edge to /BGIN rising edge                                      | t27 /      | 20         |              | ns                                               | 10       |

| /BGIN            | Rising edge to CPUCLK rising edge                                             | t27a       | 0          |              | ns                                               | 10       |

| /AS              | CPUCLK falling edge to /AS falling edge                                       | 430        |            | 18           | ns                                               | 10       |

| /AS              | CPUCLK falling edge to deassertion                                            | t31        |            | 18           | ns                                               | 10       |

| \                | of signal                                                                     |            |            |              |                                                  |          |

| /ABEN, /BGACK,   | CPUCLK rising edge to                                                         | t19        |            | 55           | ns                                               | 110      |

| R/W, SIZO, SIZI, | deassertion of signals                                                        |            |            |              |                                                  | 1        |

| FC1, MA[15-0]    | deasterion or aignais                                                         |            | l <i>J</i> |              |                                                  |          |

| D[31-0]          | Valid from CPUCLK rising edge                                                 | t32        | 60         |              | ns                                               | 10       |

| D[31-0]          | (write-cycle)                                                                 | 102        |            | ł            |                                                  |          |

| D(04_0]          |                                                                               | t33        | 15         | 75           | ns                                               | 10       |

| D[31-0]          | CPUCLK rising edge to data                                                    | 100        | 13         | 1,3          | "                                                | 1.0      |

| 204.0            | invalid (write cycle)                                                         |            | 2          | <del> </del> | ns                                               | 10       |

| D[31-0]          | Data valid setup time to CPUCLK                                               | t34        | 2          |              | 113                                              | 1.0      |

|                  | falling edge (read cycle)                                                     | 105        | 15         |              | ns                                               | 10       |

| D[31-0]          | CPUCLK rising edge to data                                                    | t35        | 15         |              | 113                                              | 1.0      |

|                  | invalid (read cycle)                                                          | 100        |            |              | <del>                                     </del> | 110      |

| /STERM           | /STERM falling edge to CPUCLK                                                 | t36        | 2          |              | ns                                               | יין      |

|                  | rising edge                                                                   |            |            | ļ            | <u> </u>                                         | 1.       |

| /STERM           | CPUCLK rising edge to /STERM                                                  | 137        | 8          | l            | ns                                               | 10       |

|                  | rising edge                                                                   |            |            |              |                                                  | +        |

| COAOMO           | Falling edge to CPUCLK                                                        | t38        | 20         | 1            | ns                                               | 10       |

| /DSACK0          |                                                                               |            |            | 1            | 1                                                | 1        |

| IDSACKU          |                                                                               |            |            |              |                                                  | 112      |

| /DSACKO          | rising edge (to be seen that cycle) CPUCLK rising edge to /DSACK0             | t39        | 20         |              | ns                                               | 10       |

|                  | rising edge (to be seen that cycle) CPUCLK rising edge to /DSACK0 rising edge |            |            |              | ns                                               |          |

| /DSACK0          | rising edge (to be seen that cycle) CPUCLK rising edge to /DSACK0 rising edge | t39        | 20         |              | ns<br>ns                                         | 10       |

|                  | rising edge (to be seen that cycle) CPUCLK rising edge to /DSACK0             |            |            |              |                                                  |          |

- Note 1: The data hold timing t35 (read cycle) is longer than the data hold timing of the 68030.

- Note 2: Careful consideration of the daisy chained /BGIN to /BGOUT signal is required when using this part in a system with more than two bus masters (other than the 68030). The delay from the breaking of the daisy chain (the time until /BGOUT) to the set up time of /BGACK (t29) must be less than the round trip delay of the daisy chain above the SCSI DMA.

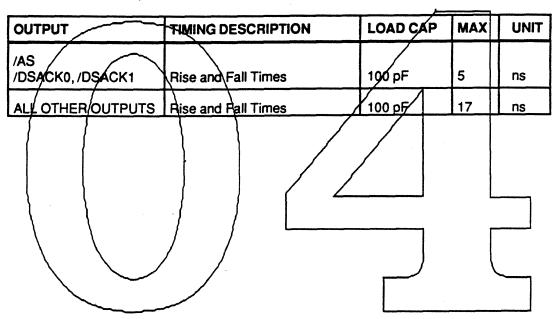

TABLE 8. OUTPUT RISE AND FALL TIME (VDD = 4.75V to 5.25V, Temperature = 0 - 70°C)

FIGURE 7. PROGRAMMED I/O WRITE TO REGISTERS TIMING

343S0064-A

FIGURE 9. PROGRAMMED I/O WRITE WITH HARDWARE HANDSHAKE TO 53C80 (WRITE REGISTER \$000)

#### SUPPLEMENTAL INFORMATION: The following is not to be used for the acceptance nor 6.0 rejection of the part herein.

The SCSI DMA chip is intended to provide a high speed interface from the 68030 bus to the ANSI Small Computer Systems Interface (SCSI) bus. It provides all the features of, and supports the software written for the 53C80 chip and in addition handles data transfers via DMA to the 68030 host processor. Only data transfers are handled by the DMA channel; other SCSI bus protocol is handled in software running on the host processor.

During Programmed I/O (PIO) mode, control and command bytes are passed to the SCSI DMA from the host at one byte per transfer. Using DMA mode, data transfers are normally 4 bytes (32 bits) per transfer.

Two eight bit registers (74F574 for example) are required external to the SCSI DMA to allow for multiplexing the address bus and thus reducing the pin count of the SCSI DMA. See Figure 5 for schematic.

### Some features of the SCSI DMA include:

- \* 53C80 host adapter cell with enhancements

- \* DMA bypass mode (to remain compatible with current software written for the 53C80)

- \* Hardware handshake mode (bytes are transferred under software control and no polling for available bytes is necessary)

- \* 32 bit DMA data transfers.

- 4 gigabyte direct addressing range (32-bit DMA address register)

- \* Block transfers of 4 gigabytes supported (32 bit DMA byte counter)

- \* Supports misaligned (non-modulo 4) data buffer addresses into "normal (not Nubus)" memory

- \* Supports non/modulo 4/DMA byte counts

- \* Programmable watchdog timer

- \* 3 MB/sec asynchronous transfer rate

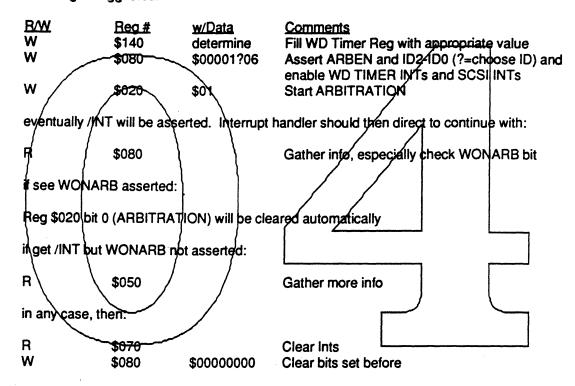

- \* Automatic SCSI bus arbitration ("old" arbitration scheme supported also)

### 6.1 THEORY OF OPERATION

#### 6.1.1 BLOCK DIAGRAMS:

Flow Block Diagram: Refer to Figure 2 (Flow Block Diagram) for the fellowing 6.1.1.1

explanations.

AIFO Input Mux/Logic: This multiplexer provides byte routing into the FIFO. The data going into the FIFO either comes from the data bus or from the 53C80.

DMA Data Out Logic: These buffers provide byte routing from the FIFO onto the processor data/bus.

FIFO Logic: The FIFO is used to assemble or disassemble 4 byte longwords from, or into-bytes.

PIO Buffer: This buffer allows control or status information to be transferred directly to the 53C80 cell.

53C80 Cell: This is an enhancement of the familiar 53C80 circuit. It will allow transfers of up to 3 megabyte/second and will also provide automatic SCSI bus arbitration.

DMA Address Counter: This counter contains the DMA address.

Address Multiplexing Buffers: These buffers allow the multiplexing of the 32 bit address into two 16 bit halves.

Address Readback Buffer: This buffer allows the DMA address to be read by the CPU.

DMA Count Counter: This counter contains the number of bytes left to transfer in the current DMA operation.

Watchdog Timer Register: This register contains the initial value of the time delay of the watchdog timer.

Watchdog Timer Counter: This counter contains the current value of the time delay of the watchdog timer.

Control State Machine: This circuitry controls all operations of the SCSI DMA chip.

- **5.1.1.2 Detailed Block Diagram:** Refer to Figure 3 (Detailed Block Diagram) for the following explanations. The Detailed Block Diagram notes the main logic blocks and their interconnections.

- Decoder: Based on state bits Q~(2:0) and other inputs, this block decodes information to supply control signals to other blocks.

- State Machine: Design's single state machine that supplies state bits Q~(2:0), control signals, and chip outputs.

- Watchdog Timer: Performs Watchdog Timer logic. Contains Watchdog Timer Register (Register \$140).

- FIFO: Performs FIFO logic. Contains FIFO Register (Register \$180).

- DMA Decoder: Based on state bits Q~(2:0) and other inputs, this block decodes information to supply DMA control signals to other blocks.

- DMA Control Register: Performs logic to update DMA Control Register (Register \$080), which is also contained in this block.

- DMA Address: Performs logic to control DMA address functions. Contains DMA Address Register (Register \$100).

- DMA Counter: Performs logic to control DMA byte counter functions. Contains DMA Count Register (Register \$0C0).

- 53080 Cell: Enhanced 53C80 cell included in SCSI DMA. Performs all SCSI transactions. Contains Registers \$070 to \$000.

- Misc. 1. Miscellaneous logic external to major blocks listed above.

- Misg. 2: Miscellaneous logic external to major blocks listed above.

#### 6.2 MODES OF OPERATION

The SCSI DMA may be operated in four modes—Slave (PIO) Mode, Master (DMA) Mode, Test Mode, and Reset Mode

- 6.2.1 Slave (PIO) Mode Operation: In Slave Mode, the SCSI DMA operates much like a 53C80 with five extra registers. The 68030 is the bus master and accesses the SCSI DMA's registers by writing to or reading from the system-defined address space of the SCSI DMA, which, through separate system logic, will assert the SCSI DMA's /CS input. The SCSI DMA looks like an asynchronous (/DSACK-driving) memory controller to the 68030 during Slave Mode. Slave Mode is utilized to perform PIO (Programmed I/O) register set-up and data transfers.

- 6.2.2 Master (DMA) Mode Operation: When the SCSI DMA operates in Master (DMA) Mode, it becomes the bus master and operates much like a less-powerful 68030. To perform DMA transfers, the SCSI DMA assumes bus mastership through the regular 68030 bus arbitration procedures and then carries out the data transfers between main memory and the SCSI Bus without 68030 assistance, thereby freeing the 68030 to perform other tasks.

- **6.2.3 Test Mode:** The SCSI DMA supports three test modes: 53C80 Isolation Test, Tri-State on Register 1 bit 6 Assertion Test, and FIFO Loopback/Internal Counters Test.

- 6.2.3.1 53C80 Isolation Test: To put the SCSI DMA into 53C80 Isolation Test mode, the TEST input must be high. In this mode, the pinout of the chip is redefined to bring internal 53C80 signals to the pads to allow 53C80 isolation tests to be performed. (See Table 3 for 53C80 Isolation Test Pinout.) This test mode is designed for use by the chip manufacturer.

- 6.2.3.2 Tri-State on Register 1 bit 6 Assertion Test: Tri-State on Register 1 bit 6 Assertion Test occurs by writing bit 6 of Register \$010 with a 1. This causes all output lines on the SCSI DMA to be held in a high impedance state until bit 6 of Register \$010 is written with a 0.

- 6.2.3.3 FIFO Loopback/Internal Counters Test: The SCSI DMA is put into FIFO Loopback/Internal Counters Test mode by writing bit 5 of Register \$080 (DMA Control Register) with a 1. This mode allows each bit of Register \$180 (FIFO Register) to be written and read. In normal operation, one can only read the contents of the FIFO Register. Also in this mode, the DMA Count, DMA Address, and Watchdog counters are connected such that each nibble of each counter will count independently and will be incremented or decremented (depending on the counter—the DMA Count and Watchdog counters decrement while the DMA Address counter increments) by a read of their respective initial-value-holding registers (Registers \$0C0, \$100, or \$140).

- 6.2.4 Reset Mode: The SCSI DMA may be reset in four ways: SCSI DMA Hardware Reset, DMA Control Register Software Reset, Initiator Command Register Software Reset, and SCSI Bus Hardware Reset.

- 6.2.4.1 SCSI DMA Hardware Reset: To reset the entire SCSI DMA chip (including the 53C80 cell) the /RESET signal must be low for at least 80 ns. Logic is included to delay the reset input to the 53C80 cell to assure that it will meet its 100 ns minimum reset-assertion-time requirement. This reset mode resets all parts of the SCSI DMA's DMA logic and registers and issues a hardware reset to the 53C80 cell.

- 5.2.4.2 DMA Control Register Software Reset: By writing bit 4 of the DMA Control Register (Register \$080) with a 1, the DMA Control Register Software Reset is employed. This reset mode essentially performs a 53C80 hardware reset, in that it causes the RESET input to the 53C80 cell to be held active long enough to meet its 100 ns minimum reset-assertion-time requirement. It is not necessary to clear bit 4 of the DMA Control Register after performing a DMA Control Register Software Reset; the 53C80 cell will only be hardware reset once per assertion of bit 4 of the DMA Control Register.

Reset is executed by writing bit 7 of the Initiator Command Register Software

Reset is executed by writing bit 7 of the Initiator Command Register (Register \$010) with

a 1. This asserts the /SRST line and the 53C80 IRQ signal, but clears all other internal

53C80 logic and registers; this essentially issues a SCSI Bus Reset through software.

To clear this situation, bit 7 of the Initiator Command Register (Register \$010) must be

written with a 0. To clear the interrupt, read Register \$070. A SCSI DMA Hardware

Reset or a DMA Control Register Software Reset will also clear bit 7, deassert /SRST,

and clear the interrupt

SCSI Bus Hardware Reset: To issue a SCSI Bus Hardware Reset, the SRST line must be driven low. This causes the 53C80 IRQ signal to also be asserted and clears all other internal 53C80 logic and registers. To clear this situation, either /SRST must be deasserted, or bit 7 of the Initiator Command Register (Register \$0 10) must be written with a 0. To clear the interrupt, read Register \$070. A SCSI DMA Hardware Reset or a DMA Control Register Software Reset will also clear bit 7, deassert /SRST, and clear the interrupt.

#### 6.3 SCSI HOST ADAPTER

An enhanced 53C80 is the SCSI host adapter. The enhancements included in this cell over the regular 53C80 are autoarbitration capability and improved asynchronous data transfer. This cell handles all SCSI bus protocol and data transfers. It is accessed directly by the host for all command and control (PIO) transfers to or from the SCSI bus. The SCSI DMA has the DMA capability to offload the host from the tedious job of transferring data byte by byte under direct processor control, although it supports this means of transfer. Refer to the 53C80 manual for details on the operation of the host adapter cell.

#### 6.4 BYTE ROUTING AND FIFO LOGIC

The purpose of the byte router logic is to interface between the 32 bit CPU data bus and the 8 bit SD (SCSI Data) bus. The SD bus is an internal 8 bit data bus connected to the 53C80 cell. The byte router logic provides support for misaligned DMA data transfers, programmed I/O (PIO) transfers directly to the 53C80, and a one long word FIFO for DMA data transfers.

#### 6.5 DMA CHANNEL

- 6.5.1 Signal Timing Scenario: The SCSI DMA can do all data transfers via direct memory access (DMA) to the processor (host) bus. After all control information is written to load up the DMA address counter and the DMA byte count and set up the 53C80 to do data transfers, the DMA operation witing to one of the DMA start registers. (See section 6.7.2.3 for details). The 53C80 requests each DMA transfer (when the FIFO is full) via the internal signal DREQ, and that request is passed to the DMA control logic. The SCSI DMA then asserts /BR (Bus Request) in order to gain bus mastership of the 68030 bus. If the processor intends to release the bus after the current bus cycle has completed, it asserts the signal /BG (bus grant) and this signal is passed to all bus masters via a daisy chain. The ASG signal will enter the SCSI DMA via the pin /BGIN. The control logic recognizes /BGIN, and after the current bus cycle has completed, the SCSI DMA asserts /BCACK to hold the bus. As soon/as it recognizes that the bus is obtained, the SCSI DMA gates the high order DMA address A(31-16) on the lines MA(15-0) and asserts /ALE. The required external register (74/574) will latch this address. The SCSLDMA then asserts /ABEN and gates the low order DMA address on the lines MA[15-0]. The signal /ABEN is used by the external register to enable the high order address onto the address bus A[31-16]. The SCSI DMA will then drive P/W, FC1, SIZ0, SIZ1, and /AS. If a read (DMA read from memory, write to SCSI) operation is requested, the SCSI DMA will latch the data from the processor data bus. If a write (DMA write to memory, read from SCSI) operation is requested, the SCSI DMA will gate the data onto the processor data bus. It is intended that all DMA transfers with memory be synchroneus on the 68030 bus (/STERM supplied by methory controller). However, the signals /DSACK0 and /BERR will also terminate a DMA data transfer.

- 6.5.2 Watchdog Timer: The watchdog timer can be used to monitor the DMA activity. If no DMA activity happens before it counts down, it will interrupt the CPU (if watchdog timer interrupts are enabled DMA Control Register bit 2 asserted) and terminate the DMA operation. Any DMA activity causes the timer to be reloaded with the value stored in the Watchdog Timer Register (Register \$140).

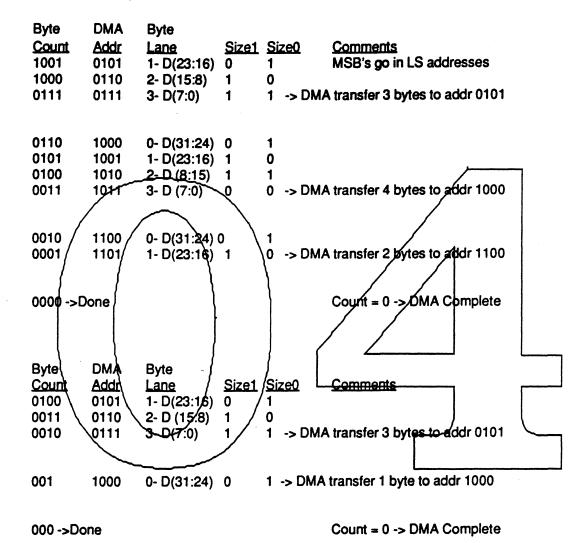

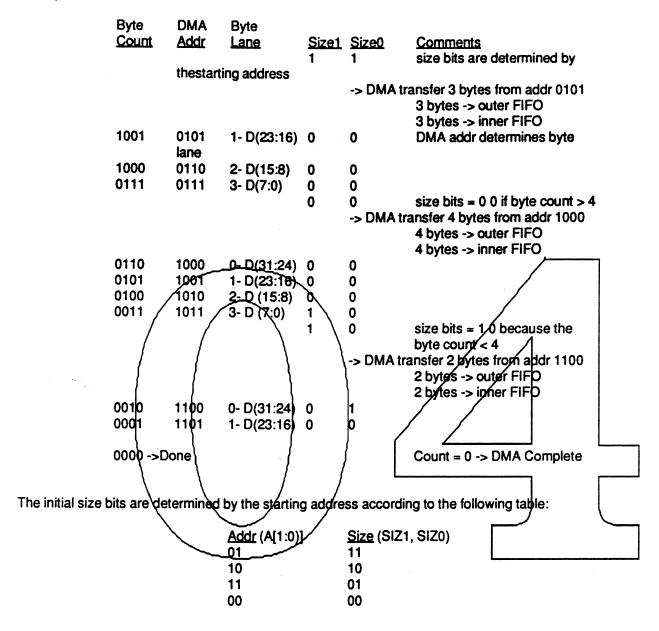

- 6.5.3 Non-Modulo 4 Transfers: The method by which the SCSI DMA handles non-modulo 4 addresses and non-modulo 4 byte counts is by adjusting for non-modulo 4 addresses on the first 68030 bus transfer and adjusting for non-modulo 4 byte counts on the last 68030 bus transfer. The address is detected to be non-modulo 4 if either or both of the least significant two address bits are non-zero. The value of these address bits determines which of the byte lanes are to be filled. The byte count is decremented by one and the address is incremented by one each time a byte is transferred to or from the 53C80. When the most significant byte lane has been filled, a 68030 DMA transfer is initiated and the size bits will be determined by the number of bytes in the FIFO. The DMA address which will be gated onto the address bus will be the current address minus the number of bytes in the FIFO. Consider the following examples:

#### Example 1: WRITE

As shown, the byte count and DMA address are changed after each byte is transferred from the 53C80 to the FIFO. The byte count is decremented by one and the address is incremented by one. The bytes are placed in the correct byte lane as they are transferred from the 53C80. The two least significant address bits of the current address determine the byte lane. As each byte is placed in its byte lane, the size counter is incremented by one. This counter contains the number of bytes in the FIFO and the number of bytes to transfer when a DMA transfer is initiated.

## Example 3

Example 2

| Byte<br><u>Count</u><br>0010<br>0001 | DMA<br><u>Addr</u><br>0101<br>0110 | Byte<br><u>Lane</u><br>1- D(23:16)<br>2- D (15:8) | 0 | <u>Size0</u><br>1<br>0 -> DM/ | Comments A transfer 2 bytes to addr 0101 |

|--------------------------------------|------------------------------------|---------------------------------------------------|---|-------------------------------|------------------------------------------|

|--------------------------------------|------------------------------------|---------------------------------------------------|---|-------------------------------|------------------------------------------|

000 ->Done

Count = 0 -> DMA Complete

#### Example 4: READ

#### **Size Output Encodings**

| Siz1 | Siz0 | Size      |

|------|------|-----------|

| 0    | 1    | Byte      |

| 1    | 0    | Word      |

| 1    | 1    | 3 Byte    |

| 0    | 0    | Long Word |

|      |      |           |

#### 6.6 MEMORY MAP AND PROGRAMMERS MODEL

Refer to Figure 11 for register memory map assignments. The memory map presupposes that the signal /CS is asserted.

#### 6.6.1 SCSI HOST ADAPTER REGISTERS (Registers \$000 - \$070)

The byte-wide 53C80 registers are mapped to address bits MA[8-4] = \$00 to \$07. Refer to the 53C80 design manual for a detailed description of each bit's function.

#### 6.6.2 FIFO REGISTER (Register \$180)

This 32 bit register contains the FIFO contents. In normal operation it may only be read. In FIFO Loopback/Internal Counters Test Mode, it may be both read and written.

# 6.6.3 WATCHDOG TIMER REGISTER (Register \$140)

This register is written with the watchdog timer count. The watchdog counter is loaded with this count and begins to count down immediately at a rate of 1/2 the frequency of the CPUCLK input. During each DMA transfer the counter is reloaded with the count. If no DMA operation occurs, no reload will take place and the watchdog counter will count down to zero. After it has counted to zero it will not continue to count. If the watchdog counter counts down to zero, it will set the WD Timer Interrupt Pending bit (bit 7 of the DMA Control Register) and generate an interrupt if WD Timer Interrupts are Enabled bit (bit 2 of the DMA Control Register) is set. Watchdog timer interrupts may be cleared by reading or writing the watchdog counter register (register \$140).

#### 6.6.4 DMA ADDRESS REGISTER (Register \$100)

This 32 bit register contains the current DMA address. It may be read or written.

# 6.6.5 DMA BYTE COUNT REGISTER (Register \$0C0)

This 32 bit register contains the current DMA byte count. It may be read or written.

# 6.6.6 DMA CONTROL/REGISTER (Register \$0,80)

This 32 bit register contains the Control and configuration information for the SC\$I DMA. The 32 bit DMA Control Register bit definitions are as follows:

| BIT   | NAME                                         | READ/WRITE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|----------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | DMA Enabled<br>SCSI Interrupts Enabled       | F/W        | ow-DMA operations disabled, high-DMA enabled ow-interrupts from DMA operations or from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2     | WD Timer Interrupts Enabled                  | RW /       | SCSI bus disabled, high-interrupts enabled low-watchdog timer interrupts disabled,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3     | Hardware Handshake Mode                      | RW         | high-interrupts enabled/ high-set hardware handshake mode, low-disable hardware handshake mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4     | 53C80 Reset/Bytes Leit in FIFO               | R/W        | write only: high-reset the 53G80 (internal cell) (does not tri-state the SCSI DMA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5     | FIFO Loopback/Internal Counters<br>Test Mode | R/W        | read only: high-indicates that bytes are left in the FIFO high-enable FIFO Loopback/Internal Counters Test mode, low-disable FIFO Loopback/Internal Counters Test mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6     | SCSI Interrupt Pending                       | R only     | high-an interrupt from the SCSI bus is pending or the DMA operation has terminated successfully                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7     | WD Timer Interrupt Pending                   | R only     | high-an interrupt from the watchdog timer is pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8     | DMA halted by bus error                      | R only     | high-the requested DMA operation has been halted due to a bus error (Clean by William Common |

| 9-11  | ID0-2                                        | R/W        | These bits are used as our SCSI Address during the arbitration phase.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12    | ARBEN                                        | R/W        | Enable autoarbitration. (See section 6.7.1 for further information on autoarbitration)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |